# Superskalare Architekturen (4)

Rechnerarchitektur, Foliensatz 10 Wintersemester 2010/11 2010/12/09 Folie [10] - 1 / 32

# Dynamische Sprungvorhersage mit "Vorgeschichte"

- (hoffentlich wieder kehrende)

Muster in Programmausführung erkennen

- exakte Historie der Verzweigungen (Taken / Not Taken) berücksichtigen, speichern in Schieberegister

- Globale / Lokale Historie:

- lokal: für jeden Verzweigungsbefehl eine separate Historie speichern

- global: nur eine einzige Historie; speichert Ergebnisse der letzten ausgeführten Verzweigungen

#### Hans-Georg Eßer, Dipl.-Math. Dipl.-Inform. Hochschule München

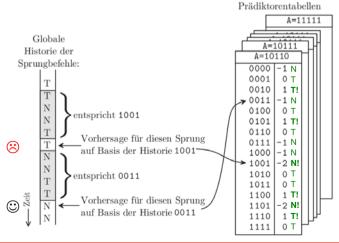

#### Globale Historie (1)

- nur ein Schieberegister für das ganze Programm (das ist das "globale")

- - Blick in Schieberegister

- Suche der richtigen Prädiktortabelle für akt. Adresse

- Sch.-Reg.-Inhalt in Prädiktortabelle suchen

Rechnerarchitektur, Foliensatz 10 Wintersemester 2010/11 2010/12/09 Folie [10] - 3 / 32

## Globale Historie (2)

#### **Lokale Historie**

- für jede Adresse (genauer: Adress-Hashing):

- **separates** Schieberegister (das ist das "lokale")

- Prädiktortabelle für diese Adresse

- So geht's:

- abhängig von Adresse: Auswahl des richtigen Schieberegisters

- Suche der richtigen Prädiktortabelle für akt. Adresse

- Sch.-Reg.-Inhalt in Prädiktortabelle suchen

Rechnerarchitektur, Foliensatz 10

Wintersemester 2010/11

2010/12/09 Folie [10] - 5 / 32

#### Beispiel: 4-stufige Historie, 2-bittige Prädiktoren

- *simple.mms* mit YesNo = 11001100...

- nur ein Sprungbefehl (eine Tabelle)

- Alle Prädiktoren auf 00 (T) initialisiert

- "leicht optimistisch", dass gesprungen wird;

- Skala: 01 = T!, 00 = T, 10 = N, 11 = N!

- Historie vor dem Start: NNNN

- Nach jedem Sprung: Prädiktor aktualisieren

#### Beispiel: 4-stufige Historie, 2-bittige Prädiktoren

| Beobach-   |          | Prädiktoren |      |      |      |             |      |

|------------|----------|-------------|------|------|------|-------------|------|

| tete Folge | Historie | NNNN        | NNNT | NNTT | NTTN | TTNN        | TNNT |

| 1. T       | NNNN     | 00 😊        | 00   | 00   | 00   | 00          | 00   |

| 2. T       | NNNT     | 01 ⊅        | 00 😊 | 00   | 00   | 00          | 00   |

| 3. N       | NNTT     | 01          | 01 7 | 00 🙁 | 00   | 00          | 00   |

| 4. N       | NTTN     | 01          | 01   | 10 🗸 | 00 🙁 | 00          | 00   |

| 5. T       | TTNN     | 01          | 01   | 10   | 10 \ | 00 ©        | 00   |

| 6. T       | TNNT     | 01          | 01   | 10   | 10   | <b>01</b> 7 | 00 © |

| 7. N       | NNTT     | 01          | 01   | 10 😊 | 10   | 01          | 01 / |

| 8. N       | NTTN     | 01          | 01   | 11 🗸 | 10 😊 | 01          | 01   |

| 9. T       | TTNN     | 01          | 01   | 11   | 11 \ | 01 ©        | 01   |

| 10. T      | TNNT     | 01          | 01   | 11   | 11   | 01          | 01 © |

Hans-Georg Eßer, Dipl.-Math. Dipl.-Inform. Hochschule München Rechnerarchitektur, Foliensatz 10 Wintersemester 2010/11 2010/12/09 Folie [10] - 16 / 32

#### **Platzbedarf**

- Adress-Hashing: a relevante Bits, 2<sup>a</sup> unterscheidbare Adressen

- Länge des/der Schieberegister: b

- *n*-bittige Prädiktoren (2 Bit: 01=**T**!, 00=**T**, 10=**N**, 11=**N**!)

#### **Lokale Historie**

#### **Globale Historie**

$$2^{a} \cdot b + 2^{a} \cdot 2^{b} \cdot n$$

$$= 2^{a} \cdot (b + 2^{b} \cdot n)$$

$2^a \cdot (b + 2^b \cdot n)$ Anzahl der Schieberegister

b + 2<sup>a</sup> · 2<sup>b</sup> · n

Anzahl Bits pro Prädiktor

Anzahl möglicher Inhalte eines

Schieberegisters

Anzahl Prädiktor-Tabellen

Länge des Schieberegisters

## Speicher (1)

Rechnerarchitektur, Foliensatz 10 Wintersemester 2010/11

2010/12/09 Folie [10] - 18 / 32

## **Speicher-Typen**

- SRAM (Static RAM)

- DRAM (Dynamic RAM)

- SDRAM (Synchronous DRAM)

- PC66/100/133: 168 Pins, 64 Datenleitungen

- DDR (Double Data Rate) PC1600/2100/2700: 184 Pins

- DDR2, DDR3: 240 Pins

Hochschule München

• SDRAM synchron (mit Takt) les-/beschreibbar

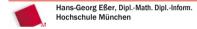

#### **Speicher-Organisation**

- zweidimensional: "Zeilen" und "Spalten"

- Einsparen von Anschlussleitungen: Zeilen- und Spaltenadresse nacheinander über die gleichen Leitungen übermitteln

- Aufeinanderfolgende Zugriffe auf die gleiche Zeile (page) erfordern kein erneutes Dekodieren / Auslesen dieser Zeile (page hit: Seite ist bereits "offen")

- Bänke: erlauben parallele Zugriffe auf Chip

Rechnerarchitektur, Foliensatz 10 Wintersemester 2010/11

2010/12/09 Folie [10] - 20 / 32

## **Speicherzugriff**

Wintersemester 2010/11

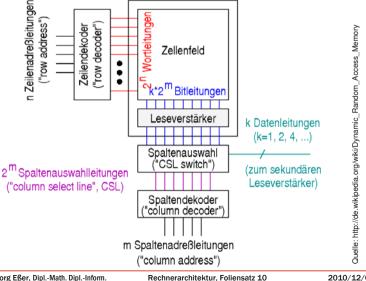

#### **Speicherhierarchie**

Rechnerarchitektur, Foliensatz 10 Wintersemester 2010/11 2010/12/09 Folie [10] - 22 / 32

## **Caching**

- Cache: sehr schneller Speicher

- speichert kürzlich verwendete RAM-Inhalte zwischen

- beschleunigt erneuten Zugriff auf dieselbe Speicherzelle

- muss Paare (Adresse, Inhalt) speichern

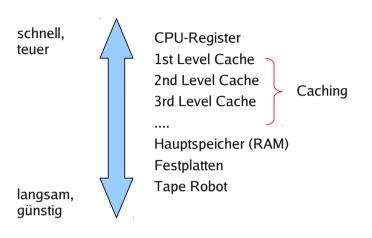

- · Zugriff auf Cache

- gewünschte Adresse anlegen

- Antwort sofort (assoziativer Speicher):

Inhalt (cache hit) oder Fehler (cache miss)

#### **Caching**

- Cache enthält immer ganze **Cache-Line** (Block von Speicheradressen, die sich nur in den unteren *b* Bits unterscheiden)

- Simultaner Vergleich aller "Tags" mit oberen w b Bits der angeforderten Adresse

#### **Caching**

- Alternativ zu assoziativem Speicher: direkt-abbildender Cache

- Cache besteht aus *n* Blöcken C[i]

- RAM "partitioniert" in *n* gleich große Teile R[i]

- RAM-Inhalte aus R[i] in C[i] ablegen

- einfacher als assoziativer Speicher, aber schlechtere Ausnutzung des Cache-Speichers

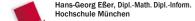

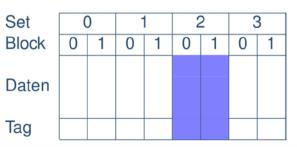

### **Caching**

- Kombination der beiden Caching-Methoden

- Cache in 2<sup>c</sup> sog. **Sets** unterteilt

- jedes Set besteht aus  $n = 2^a$  Blöcken der Größe  $2^b$

- Set-Nummer (a-bittig): **Index**, **Set-Adresse**

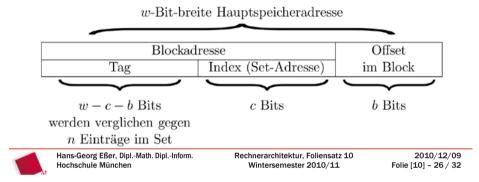

#### Varianten direkt-abb./assoz. (1)

- voll-assoziativer Cache

- nur 1 Set (c = 0)

- Block an beliebiger Position speichern

#### Hans-Georg Eßer, Dipl.-Math. Dipl.-Inform. Hochschule München

#### 2010/12/09 Folie [10] - 27 / 32

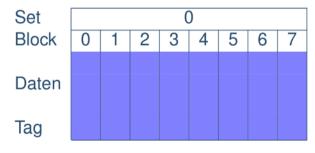

#### Varianten direkt-abb./assoz. (2)

- Direkt abbildender Cache

- enthält in jedem Set nur einen Block: a = 0

- Block immer nur an eine feste Position schreibbar

Hans-Georg Eßer, Dipl.-Math. Dipl.-Inform. Hochschule München Rechnerarchitektur, Foliensatz 10 Wintersemester 2010/11 2010/12/09 Folie [10] - 28 / 32

#### Varianten direkt-abb./assoz. (3)

- n-way associative cache

- Sets mit je *n* Blöcken

- Beispiel n = 2: 2-Wege-assoziativer Cache

- Set durch Adresse festgelegt; in Set freie Wahl

#### **Allgemeines zum Caching**

- Bei Speicherzugriffen sucht die CPU zuerst im Cache

- Wird sie dort nicht fündig (cache miss), muss sie auf den Hauptspeicher zugreifen (was deutlich länger dauert)

- Lokalitätsprinzip: Zugriffe bleiben häufig "in der Nähe" von bereits verwendeten Adressen

- → darum auch kleine Caches hilfreich

- kein Platz im Cache? → Verdrängung

Rechnerarchitektur, Foliensatz 10 Wintersemester 2010/11 2010/12/09 Folie [10] - 30 / 32

### **Cache: Schreibzugriffe**

- Write through: Daten werden gleichzeitig in den Cache und die nächst niedrigere Speicherhierarchie geschrieben.

- Write back: Daten werden nur in den Cache geschrieben. Entsprechender Block wird dort als "dirty" gekennzeichnet. Rückschreiben erst erforderlich, wenn der Block ersetzt werden soll (hier kann also ein Lesevorgang einen Schreibvorgang auslösen). Spart Speicherbandbreite, ist aber aufwendiger zu realisieren

#### Vorschau 16.12.2010

mehr Caching: Verdrängung

Rechnerarchitektur, Foliensatz 10 Wintersemester 2010/11 2010/12/09 Folie [10] - 32 / 32